# D.N.R.COLLEGE(AUTONOMOUS)::BHIMAVARAM

## **M.Sc COMPUTER SCEINCE DEPARTMENT**

I - M.Sc(CS)

I SEMSETER

**E-CONTENT**

## **COMPUTER ORGANIZATION AND ARCHITECTURE**

Presented by **K.VENKATESH**

#### COMPUTER ORGANIZATION AND ARCHITECTURE(MSCS 103)

| Theory  | : 4 Periods | Mid Marks 🛛 🔁 🎝 🎝 🍾 🍾 🍾 🎝 🍅 |

|---------|-------------|-----------------------------|

| Lab Hrs | : 0 Periods | Ext. Marks 4                |

| Exam    | : 3 Hrs.    | Credits :                   |

#### Unit I

Basic Structure of computers: Computer types,Functional units,Basic Operational concepts,Bus Structures, Software,Performance,Multiprocessors and Multi-computers,Historical perspective,Machine Instructions and Programs,Memory locations and Addresses,Memory Operations,Instructions and Instruction sequencing,Addressing modes,Assembly language,basic input and output operations,stacks and queues,Subroutines,Additional instructions,Example programs,Encoding of Machine Instructions.

#### Unit II

Input/output/organization: Accessing I/O devices, Interrupts, Processor Examples, Direct Memory Access.Interface circuits,Standard I/Ointerfaces.The Memory system:some basic concepts, semiconductor RAM Memories, ROM memories, speed, size and cost,Cache Memories, Performance Memories, Memory Considerations, Virtual Management Requirements, Secondary Storage. Basic Processing Unit: Some fundamental concepts, Execution of Complete Instruction, Multiple Bus Organization, Hardwired control, Micro programmed control.

#### Unit III

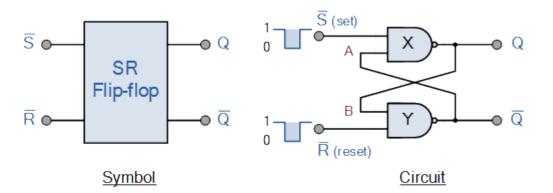

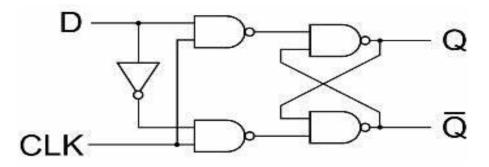

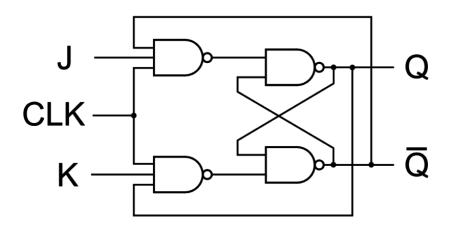

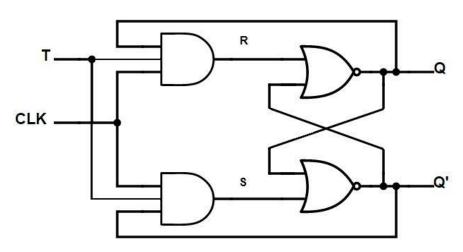

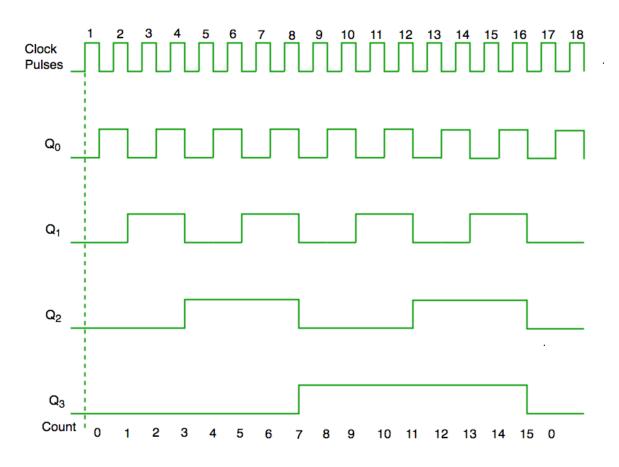

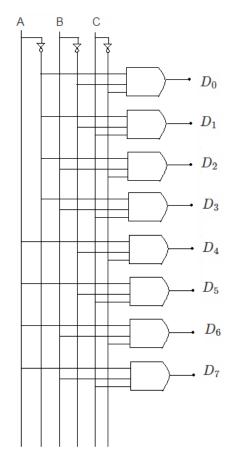

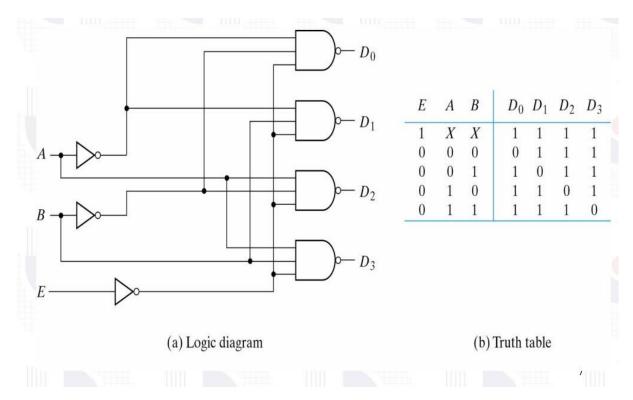

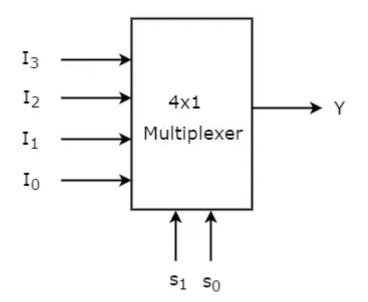

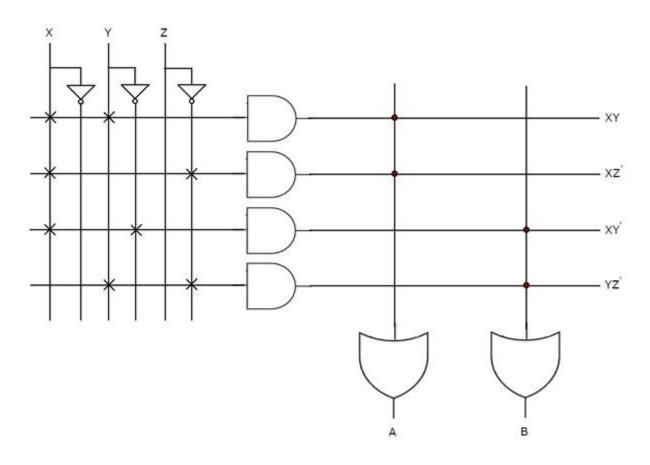

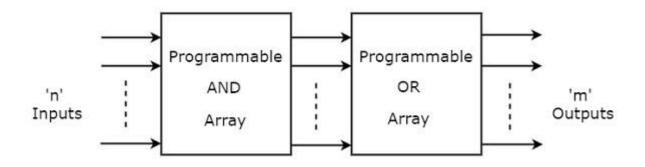

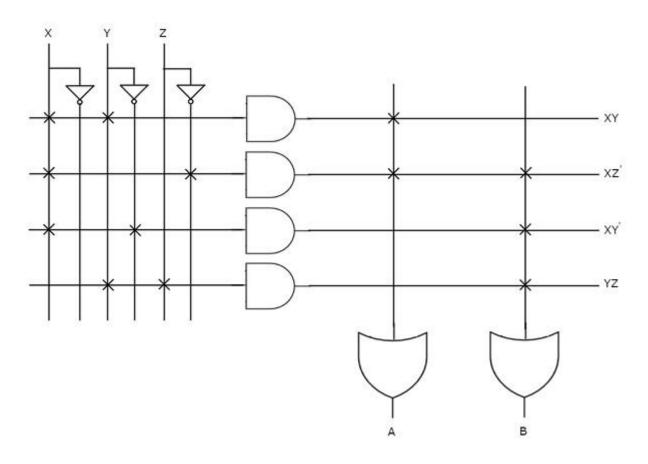

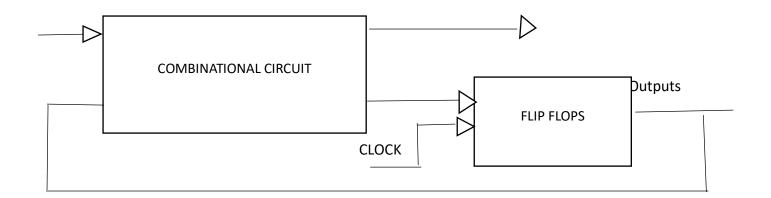

Peripherals:Input Devices,Output Devices,Serial Communication Links,Large Computer Computer Systems:Forms of Parallel Processing, Array Processors, The structure of Multiprocessor, Interconnection networks, Memory organization in multiprocessors, Program parallelism and shared variables, Multicomputers. Logic circuits: Basic logic functions, Synthesis of Logic functions, Minimization of Logic, Synthesis with NAND and NOR gates, Practical implementation of Logic gates,Flip flops,Registers and shift registers, Counters, Decoders, Multiplexers, PLD, Sequential circuits.

#### Unit IV

Hazards, Instruction Pipelining:Basic concepts,Data Hazards, Influence on Instruction sets, Superscalar operation. Examples of Embedded Systems, Processor chips for embedded Microcontroller, The applications,A simple IA-32 Pentium example:Registers and Addressing, IA-32 Instructions, IA-32 Assembly language, Program flow control, Logic and shift /Rotate instructions,I/O Operations,Subroutines,other instructions,Program examples.

Text Book:

1. Computer Organization,carlhamacher,ZvonkoVranesic,Safwatzaky, McGraw Hill Publications

## <u>UNIT 1</u>

## **Introduction To The Basic Structure Of Computers**

I The Basic Structure Of Computers Refers To The Organization And Components That Collectively Enable A Computer System To Function. This Structure Encompasses Both Hardware And Software Components, Each Playing Critical Roles In Processing Information And Executing Tasks. Here's An Overview Of The Basic Structure Of Computers In CO:

#### **1. HARDWARE COMPONENTS:**

#### 1.1. Central Processing Unit (CPU):

**Function:** The CPU Is The Core Component Responsible For Executing Instructions And Coordinating The Activities Of Other Hardware Components.

#### **Components:**

Arithmetic Logic Unit (ALU): Performs Arithmetic And Logical Operations.

**Control Unit (CU):** Manages The Execution Of Instructions, Fetches Instructions From Memory, Decodes Them, And Controls Data Flow Within The CPU And Between Other Components.

**Registers:** Small, High-Speed Storage Locations Inside The CPU Used To Store Data, Addresses, And Control Information Temporarily During Execution.

#### 1.2. MEMORY:

**Function:** Memory Stores Data And Instructions That The CPU Accesses During Program Execution.

#### **Types Of Memory:**

**Primary Memory (Main Memory):** Includes Random Access Memory (RAM) And Cache Memory. RAM Is Volatile And Stores Data And Instructions Currently In Use.

**Secondary Memory:**Includes Hard Drives, Ssds, And Other Storage Devices. It Stores Data And Instructions Persistently.

#### 1.3. Input/Output (I/O) Devices:

**Function:** I/O Devices Allow The Computer To Interact With The External World, Enabling Input (E.G., Keyboards, Mice) And Output (E.G., Monitors, Printers) Operations.

**Interface:** Controllers And Interfaces Manage Communication Between The CPU And I/O Devices.

#### 1.4. System Bus

**Function:** The System Bus Is A Communication Pathway That Connects All Components Of The Computer, Allowing Data And Instructions To Be Transferred Between CPU, Memory, And I/O Devices.

**Components:** Address Bus (For Specifying Memory Addresses), Data Bus (For Transferring Data), And Control Bus (For Managing The Timing And Control Signals).

#### 2. SOFTWARE COMPONENTS

#### 2.1. Operating System (OS)

**Function:** The OS Manages Hardware Resources, Provides A User Interface, And Facilitates Communication Between Software And Hardware Components.

Examples: Windows, Macos, Linux, Unix.

#### 2.2. APPLICATION SOFTWARE

Function: Applications Perform Specific Tasks For Users Or Other Software Systems.

Examples: Word Processors, Web Browsers, Games, And Enterprise Software.

#### 2.3. FIRMWARE AND BIOS/UEFI

**Function**: Firmware Provides Low-Level Control For Specific Hardware Components, While BIOS (Basic Input/Output System) Or UEFI (Unified Extensible Firmware Interface) Initializes Hardware During The Boot Process.

#### **3. Basic Operation Cycle**

#### **3.1. Fetch-Decode-Execute Cycle**

Fetch: The CPU Fetches Instructions From Memory.

Decode: The CPU Decodes Instructions Into Operations.

**Execute:** The CPU Executes The Decoded Instructions, Manipulating Data As Required.

#### **4. STRUCTURE IN ACTION**

#### **4.1. BOOT PROCESS**

Initialization: The BIOS Or UEFI Performs Power-On Self Test (POST) And Initializes Hardware.

Loading OS: The OS Is Loaded From Secondary Storage Into Memory.

**Execution:**Applications Run On The OS, Utilizing CPU, Memory, And I/O Devices.

#### 4.2. Processing Tasks

Execution: CPU Executes Instructions Fetched From Memory.

**Memory Access:** Data And Instructions Are Stored And Retrieved From Primary And Secondary Memory.

**I/O Operations:** Input And Output Operations Are Managed Through I/O Devices And Their Controllers.

## **Types Of Computers:**

Computers Come In Various Types And Sizes, Each Designed To Meet Specific Needs And Perform Particular Tasks. Below Is An Overview Of The Different Types Of Computers, Ranging From The Smallest Personal Devices To The Largest Supercomputers.

## **1. Personal Computers (Pcs):**

Personal Computers Are Designed For Individual Use. They Are Versatile And Capable Of Performing A Wide Range Of Tasks Such As Word Processing, Internet Browsing, Gaming, And Multimedia Playback. There Are Several Subcategories Within Personal Computers:

**Desktops:** These Are Stationary Computers Designed To Fit On Or Under A Desk. They Typically Consist Of A Separate Monitor, Keyboard, And Mouse.

**Laptops:** Portable Computers That Integrate The Monitor, Keyboard, And Internal Components Into A Single Unit. They Are Suitable For Mobile Use.

**Net Books:** Smaller, Lightweight, And Less Powerful Than Traditional Laptops, Designed Primarily For Web Browsing And Basic Tasks.

**Workstations:** High-Performance Desktops Designed For Technical Or Scientific Applications Requiring Significant Computing Power, Such As 3D Rendering Or Complex Calculations.

#### 2. Mobile Devices

These Are Portable Computing Devices With A High Degree Of Mobility. They Include:

**Smartphones:** Handheld Devices That Combine The Functionality Of A Mobile Phone With Computing Capabilities. They Run Mobile Operating Systems And Can Perform A Wide Range Of Functions Through Apps.

**Tablets:** Larger Than Smartphones, Tablets Are Touch-Screen Devices That Can Function Similarly To Both Smartphones And Laptops.

**Wearables:** Devices Such As Smartwatches And Fitness Trackers That Can Perform Computing Tasks And Interact With Other Devices.

#### **3.Servers:**

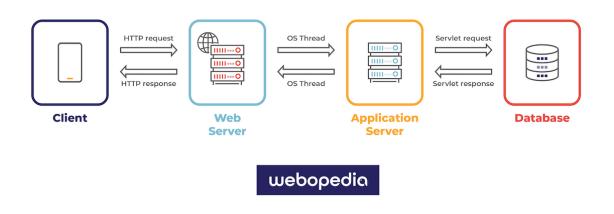

Servers Are Computers Designed To Provide Services To Other Computers Over A Network. They Handle Tasks Such As Hosting Websites, Managing Databases, And Running Applications. Types Of Servers Include:

-File Servers: Store And Manage Files For Networked Devices.

Web Servers: Host Websites And Deliver Web Content.

Database Servers: Provide Database Services To Other Computers.

Application Servers: Run Specific Applications For Client Devices.

#### 4. Mainframes:

Mainframes Are Powerful Computers Used Primarily By Large Organizations For Critical Applications, Bulk Data Processing, And Large-Scale Transaction Processing. They Are Known For Their High Reliability, Extensive Input/Output Capabilities, And Ability To Handle Massive Amounts Of Data.

#### 5.Supercomputers:

Supercomputers Are The Most Powerful Computers In Terms Of Processing Capacity. They Are Used For Highly Complex Computations That Require Immense Processing Power, Such As Climate Modeling, Scientific Simulations, And Cryptography. Supercomputers Can Perform Billions Or Trillions Of Calculations Per Second.

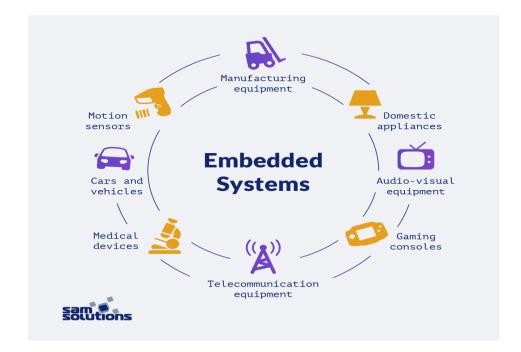

6. Embedded Systems:

Embedded Systems Are Specialized Computing Systems That Are Part Of Larger Devices. They Perform Dedicated Functions And Are Optimized For Specific Tasks. Examples Include:

Microcontrollers: Used In Household Appliances, Automobiles, And Industrial Machines.

**Embedded Controllers:** Found In Devices Like Washing Machines, Medical Devices, And Consumer Electronics.

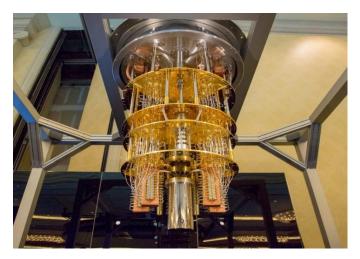

### 7. Quantum Computers:

Quantum Computers Are An Emerging Type Of Computer That Use The Principles Of Quantum Mechanics To Process Information. They Have The Potential To Solve Certain Types Of Problems Much Faster Than Classical Computers By Leveraging Quantum Bits (Qubits) That Can Exist In Multiple States Simultaneously.

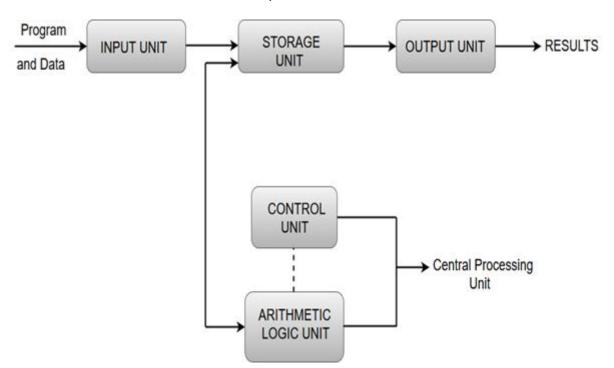

#### **Functional Unit:**

- A Computer Organization Describes The Functions And Design Of The Various Units Of A Digital System.

- A General-Purpose Computer System Is The Best-Known Example Of A Digital System. Other Examples Include Telephone Switching Exchanges, Digital Voltmeters, Digital Counters, Electronic Calculators And Digital Displays.

- Computer Architecture Deals With The Specification Of The Instruction Set And The Hardware Units That Implement The Instructions.

- Computer Hardware Consists Of Electronic Circuits, Displays, Magnetic And Optic Storage Media And Also The Communication Facilities.

- Functional Units Are A Part Of A CPU That Performs The Operations And Calculations Called For By The Computer Program.

- Functional Units Of A Computer System Are Parts Of The CPU (Central Processing Unit) That Performs The Operations And Calculations Called For By The Computer Program. A Computer Consists Of Five Main Components Namely, Input Unit, Central Processing Unit, Memory Unit Arithmetic & Logical Unit, Control Unit And An Output Unit.

# Input Unit

- Input Units Are Used By The Computer To Read The Data. The Most Commonly Used Input Devices Are Keyboards, Mouse, Joysticks, Trackballs, Microphones, Etc.

- However, The Most Well-Known Input Device Is A Keyboard. Whenever A Key Is Pressed, The Corresponding Letter Or Digit Is Automatically Translated Into Its Corresponding Binary Code And Transmitted Over A Cable To Either The Memory Or The Processor.

# **Central Processing Unit**

Central Processing Unit Commonly Known As CPU Can Be Referred As An Electronic Circuitry Within A Computer That Carries Out The Instructions Given By A Computer Program By Performing The Basic Arithmetic, Logical, Control And Input/Output (I/O) Operations Specified By The Instructions.

# Memory Unit

- The Memory Unit Can Be Referred To As The Storage Area In Which Programs Are Kept Which Are Running, And That Contains Data Needed By The Running Programs.

- The Memory Unit Can Be Categorized In Two Ways Namely, Primary Memory And Secondary Memory.

- It Enables A Processor To Access Running Execution Applications And Services That Are Temporarily Stored In A Specific Memory Location.

- Primary Storage Is The Fastest Memory That Operates At Electronic Speeds.

Primary Memory Contains A Large Number Of Semiconductor Storage Cells,

Capable Of Storing A Bit Of Information. The Word Length Of A Computer Is

Between 16-64 Bits.

- It Is Also Known As The Volatile Form Of Memory, Means When The Computer Is Shut Down, Anything Contained In RAM Is Lost.

- Cache Memory Is Also A Kind Of Memory Which Is Used To Fetch The Data Very Soon. They Are Highly Coupled With The Processor.

- The Most Common Examples Of Primary Memory Are RAM And ROM.

- Secondary Memory Is Used When A Large Amount Of Data And Programs Have To Be Stored For A Long-Term Basis.

- It Is Also Known As The Non-Volatile Memory Form Of Memory, Means The Data Is Stored Permanently Irrespective Of Shut Down.

- The Most Common Examples Of Secondary Memory Are Magnetic Disks, Magnetic Tapes, And Optical Disks.

## Arithmetic & Logical Unit

Most Of All The Arithmetic And Logical Operations Of A Computer Are Executed In The ALU (Arithmetic And Logical Unit) Of The Processor. It Performs Arithmetic Operations Like Addition, Subtraction, Multiplication, Division And Also The Logical Operations Like AND, OR, NOT Operations.

ADVERTISEMENT

## Control Unit

- The Control Unit Is A Component Of A Computer's Central Processing Unit That Coordinates The Operation Of The Processor. It Tells The Computer's Memory, Arithmetic/Logic Unit And Input And Output Devices How To Respond To A Program's Instructions.

- The Control Unit Is Also Known As The Nerve Center Of A Computer System.

- Let's Us Consider An Example Of Addition Of Two Operands By The Instruction Given As Add LOCA, RO. This Instruction Adds The Memory Location LOCA To The Operand In The Register RO And Places The Sum In The Register RO. This Instruction Internally Performs Several Steps.

# Output Unit

- The Primary Function Of The Output Unit Is To Send The Processed Results To The User. Output Devices Display Information In A Way That The User Can Understand.

- Output Devices Are Pieces Of Equipment That Are Used To Generate Information Or Any Other Response Processed By The Computer. These Devices Display Information That Has Been Held Or Generated Within A Computer.

• The Most Common Example Of An Output Device Is A Monitor.

#### **BASIC OPERATIONAL CONCEPTS:**

In Computer Organization (CO), Basic Operational Concepts Refer To The Fundamental Principles And Processes That Define How A Computer System Operates. These Concepts Are Crucial For Understanding How Computers Execute Instructions And Manage Data. Here Are The Key Operational Concepts In Computer Organization:

#### **1. Instruction Execution Cycle:**

**Fetch:** The Control Unit Retrieves An Instruction From Memory Based On The Address Held In The Program Counter (PC).

**Decode:** The Fetched Instruction Is Decoded To Determine The Operation To Be Performed And The Operands Involved.

**Execute:** The Decoded Instruction Is Executed By The Appropriate Functional Units (E.G., ALU For Arithmetic Operations).

**Store:** The Result Of The Execution Is Stored In The Appropriate Location (E.G., A Register Or Memory).

#### 2. Data Path:

- The Route That Data Follows Within The CPU During Instruction Execution, Typically Involving Registers, The ALU, And Memory.

- The Data Path Includes Buses, Which Are Used To Transfer Data Between Components.

#### 3. Control Path:

- The Sequence Of Control Signals Generated By The Control Unit To Direct The Operation Of The CPU And Other Components.

- The Control Path Ensures That Each Step Of The Instruction Cycle Is Performed Correctly And In The Right Order.

#### 4. Memory Hierarchy:

- Organizes Storage In A Hierarchy Based On Speed And Size, With Registers Being The Fastest And Smallest, Followed By Cache, Main Memory (RAM), And Secondary Storage (E.G., Hard Drives, Ssds).

- The Hierarchy Helps Balance The Trade-Off Between Speed And Cost.

#### 5. Instruction Set Architecture (ISA):

- Defines The Set Of Instructions That A Processor Can Execute.

- Includes The Instruction Formats, Addressing Modes, And Supported Data Types.

#### 6. Addressing Modes:

- Methods Used To Specify Operands For Instructions.

- Common Addressing Modes Include Immediate, Direct, Indirect, Register, And Indexed.

#### 7. Pipelining:

- A Technique That Allows Overlapping Of Instruction Execution To Improve CPU Throughput.

- The Instruction Cycle Is Divided Into Stages (E.G., Fetch, Decode, Execute), And Multiple Instructions Are Processed Simultaneously At Different Stages.

#### 8. Parallelism:

- Utilizes Multiple Processing Elements To Perform Computations Concurrently.

- Includes Techniques Like Multi-Core Processors, SIMD (Single Instruction, Multiple Data), And MIMD (Multiple Instruction, Multiple Data).

#### 9. Branching And Control Flow:

- Mechanisms To Alter The Sequence Of Instruction Execution Based On Conditions (E.G., If-Else Statements, Loops).

- Includes The Use Of Branch Instructions And Jump Instructions.

#### **10. Interrupts And Exception Handling:**

- Mechanisms To Handle Events That Require Immediate Attention From The CPU (E.G., I/O Requests, Hardware Malfunctions).

- Interrupts Temporarily Halt The Current Execution, Save The State, And Execute An Interrupt Service Routine (ISR).

#### 11. I/O Operations:

- Methods For Data Transfer Between The CPU And Peripheral Devices.

- Includes Programmed I/O, Interrupt-Driven I/O, And Direct Memory Access (DMA).

#### Diagram Of Basic Operational Concepts:

Instruction Fetch  $\downarrow$ Instruction Decode  $\downarrow$ Execute Instruction  $\downarrow$ Memory Access/Store Result  $\downarrow$ Next Instruction

Key Points In A Computer System's Operation:

- Program Counter (PC): Holds The Address Of The Next Instruction To Be Executed.

- Instruction Register (IR): Holds The Current Instruction Being Executed.

- General-Purpose Registers: Temporarily Hold Data And Intermediate Results.

- ALU Operations: Perform Calculations And Logical Comparisons.

- **Control Signals:** Direct The Timing And Execution Of Operations Within The CPU And Other Components.

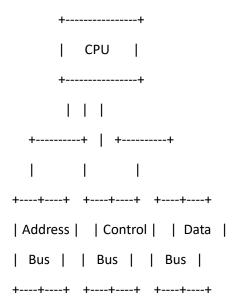

#### **BUS STRUCTURE:**

In Computer Organization, Bus Structures Are Critical Components That Facilitate Communication Between Different Parts Of A Computer System. A Bus Is A Shared Communication Pathway That Connects Multiple Subsystems, Allowing Data To Be Transferred Between Them. The Main Types Of Bus Structures In Computer Organization Include:

#### 1. Data Bus:

- Purpose: Carries Actual Data Between The CPU, Memory, And Peripheral Devices.

- Width: Determines How Many Bits Can Be Transferred Simultaneously. Common Widths Are 8-Bit, 16-Bit, 32-Bit, And 64-Bit.

- Bidirectional: Can Transfer Data In Both Directions (To And From The CPU).

#### 2. Address Bus:

- **Purpose:** Carries The Addresses Of Data (Not The Data Itself) So That The CPU Can Specify Where To Read From Or Write To In Memory.

- Width: Determines The Maximum Addressing Capacity. For Example, A 32-Bit Address Bus Can Address (2^{32}) Memory Locations.

- Unidirectional: Typically, It Only Goes From The CPU To Memory And I/O Devices.

#### 3. Control Bus:

- **Purpose:** Carries Control Signals From The CPU To Other Components To Coordinate And Manage The Operations Of The Computer System.

- **Signals:** Includes Signals For Read/Write Operations, Interrupt Requests, Clock Signals, And Status Signals.

- **Bidirectional:** Some Control Signals May Be Bidirectional, Depending On The System Architecture.

#### 4. System Bus:

- **Purpose:** A Single Bus That Combines The Data, Address, And Control Buses Into One System Bus.

- Components: Typically Consists Of Three Main Buses:

- Data Bus

- Address Bus

- Control Bus

#### 5. Expansion Bus:

- **Purpose:** Allows Additional Devices (Like Graphics Cards, Sound Cards, And Network Cards) To Be Connected To The Computer System.

- Types:

- PCI (Peripheral Component Interconnect): Used For Connecting Peripheral Devices.

- PCI Express (Pcie): A High-Speed Bus For Modern Peripheral Devices.

- ISA (Industry Standard Architecture): An Older Bus Standard.

#### 6. Backplane Bus:

- **Purpose:** Used In Systems Where Various Boards Or Modules Are Connected Via A Common Bus In A Backplane Configuration.

- **Application:** Common In Servers And Workstations Where Multiple Circuit Boards Need To Communicate.

#### 7. Local Bus:

- **Purpose:** Connects High-Speed Devices Directly To The CPU For Faster Communication, Bypassing The System Bus.

- **Examples:** The Front-Side Bus (FSB) In Older Systems, Connecting The CPU To The Memory Controller.

#### 8. Front-Side Bus (FSB):

- Purpose: Connects The CPU To The Main Memory And Other Components In Older Computer Architectures.

- Replacement: In Modern Systems, The FSB Is Often Replaced By Point-To-Point Connections Like Intel's Quickpath Interconnect (QPI) Or AMD's Hypertransport.

Diagram Of Bus Structures:

|     | I      | I      | I |     |      |   |

|-----|--------|--------|---|-----|------|---|

| +-  | ++     | +      | + | +   | +    | + |

| I   | Memory | 1/0    |   |     | I/O  | Ι |

| I   |        | Device | I | Dev | vice | I |

| +-  |        | +      | + |     | +    | - |

| ••• |        |        |   |     |      |   |

#### **Key Concepts:**

- **Bus Width:** The Number Of Lines In A Bus, Affecting The Amount Of Data That Can Be Transmitted At One Time.

- Bus Speed: The Frequency At Which The Bus Operates, Affecting Data Transfer Rates.

- **Bus Protocol:** The Rules And Methods Used For Data Transfer Over The Bus, Including Timing, Control Signals, And Data Sequences.

#### Software

In Computer Organization, Software Plays A Crucial Role In Managing Hardware Resources And Providing An Interface For User Interaction. The Key Categories Of Software In Computer Organization Include System Software, Application Software, And Programming Languages. Here's A Detailed Look At Each Category:

#### 1. System Software:

System Software Serves As A Bridge Between The Hardware And The Users. It Manages Hardware Operations And Provides A Platform For Application Software To Run.

### **Operating System (OS):**

- **Functions:** Manages Hardware Resources (CPU, Memory, I/O Devices), Provides User Interfaces (CLI Or GUI), Handles File Management, Process Management, And System Security.

- **Examples:** Windows, Macos, Linux, Unix.

**Device Drivers:**

- **Functions:** Facilitate Communication Between The OS And Hardware Devices. Each Driver Is Specific To A Particular Hardware Component.

- **Examples:** Drivers For Printers, Graphic Cards, Network Cards.

#### Firmware:

- Functions: Low-Level Software Embedded In Hardware Components, Providing Control And Basic Functionalities.

- Examples: BIOS/UEFI In Computers, Firmware In Routers.

#### Utilities:

- Functions: Provide System Maintenance And Optimization Tools.

- Examples: Disk Cleanup Tools, Antivirus Programs, Backup Utilities.

#### 2. Application Software:

Application Software Includes Programs Designed For End-Users To Perform Specific Tasks.

#### **Productivity Software:**

- Examples: Microsoft Office (Word, Excel, Powerpoint), Google Workspace (Docs, Sheets, Slides).

#### Web Browsers:

- Examples: Google Chrome, Mozilla Firefox, Microsoft Edge, Safari.

#### Media Players:

- Examples: VLC Media Player, Windows Media Player, Itunes.

### **Communication Software:**

- Examples: Email Clients (Outlook, Thunderbird), Messaging Apps (Whatsapp, Slack).

#### **Graphics And Design Software:**

- Examples: Adobe Photoshop, Illustrator, Coreldraw.

#### **Educational Software:**

- Examples: Khan Academy, Duolingo, Educational Games.

#### 3. Programming Languages And Development Tools:

These Tools Are Used To Write, Test, And Maintain Software Applications And System Software.

#### **PROGRAMMING LANGUAGES:**

- High-Level Languages: Easy To Read And Write, Closer To Human Language.

- **Examples:** Python, Java, C++, Javascript, Ruby.

- Low-Level Languages: Closer To Machine Language, Offering More Control Over Hardware.

- Examples: Assembly Language, C.

#### Integrated Development Environments (Ides):

- **Functions:** Provide Comprehensive Facilities To Programmers For Software Development, Including Code Editor, Debugger, And Compiler.

- Examples: Visual Studio, Eclipse, Pycharm, Intellij IDEA.

#### **Compilers And Interpreters:**

- **Functions:** Convert High-Level Programming Languages Into Machine Code (Compilers) Or Execute The Code Directly (Interpreters).

- Examples: GCC (GNU Compiler Collection), Java Virtual Machine (JVM).

#### 4. Middleware:

Middleware Software Provides Common Services And Capabilities To Applications Beyond Those Offered By The Operating System.

#### Functions:

- Enables Communication And Data Management For Distributed Applications.

- Facilitates Interoperability Between Different Software Applications.

- Manages And Supports Application Services Like Messaging, Authentication, And API Management.

#### Examples:

- Application Servers (Apache Tomcat, IBM Websphere).

- Database Middleware (ODBC, JDBC).

- Message-Oriented Middleware (Apache Kafka, Rabbitmq).

#### **PERFORMANCE:**

Performance In Computer Organization (CO) Refers To How Effectively A Computer System Executes Tasks, Processes Data, And Responds To User Commands. Key Factors Influencing Performance Include The Speed, Efficiency, And Throughput Of The System. Understanding These Factors Is Essential For Optimizing And Evaluating Computer Systems. Here Are The Primary Aspects Of Performance In Computer Organization:

#### 1. Clock Speed:

- **Definition:** The Frequency At Which A CPU Executes Instructions, Measured In Hertz (Hz).

- **Impact:** Higher Clock Speeds Generally Mean More Instructions Can Be Executed Per Second, Improving Performance.

- **Considerations:** Power Consumption And Heat Generation Increase With Higher Clock Speeds.

### 2. Instruction Set Architecture (ISA):

- **Definition:** The Set Of Instructions That A CPU Can Execute.

- Impact: A Well-Designed ISA Can Improve Performance By Enabling More Efficient Instruction Execution And Better Utilization Of CPU Resources.

- **Examples:** RISC (Reduced Instruction Set Computer) And CISC (Complex Instruction Set Computer) Architectures.

#### 3. Pipelining:

- **Definition:** A Technique That Allows Overlapping Of Instruction Execution By Dividing The Instruction Cycle Into Stages.

- Impact: Increases Instruction Throughput And CPU Efficiency.

- **Stages:** Common Stages Include Fetch, Decode, Execute, Memory Access, And Write-Back.

#### 4. Parallelism:

- Definition: Executing Multiple Instructions Or Processes Simultaneously.

- Types:

- Instruction-Level Parallelism (ILP): Multiple Instructions Are Executed In Parallel Within A Single CPU Core.

- **Data-Level Parallelism (DLP):** Same Operation Is Performed On Multiple Data Points Simultaneously (E.G., SIMD).

- Task-Level Parallelism (TLP): Different Tasks Or Processes Are Executed In Parallel (E.G., Multi-Core Processors).

- Impact: Improves Overall System Throughput And Performance.

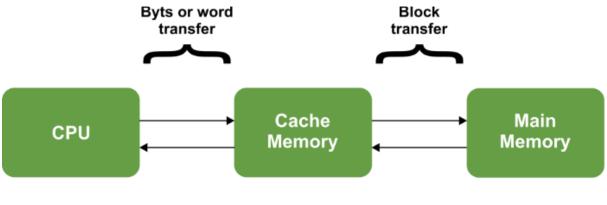

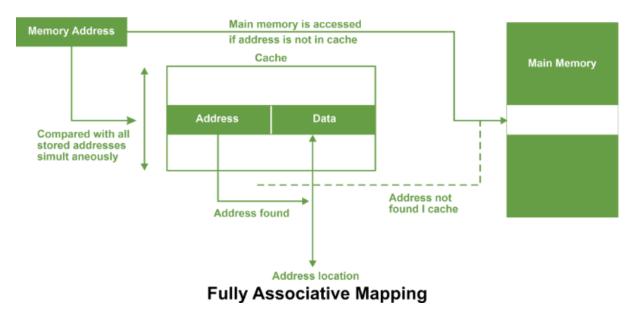

#### 5. Cache Memory:

- **Definition:** A Small, Fast Memory Located Close To The CPU To Store Frequently Accessed Data And Instructions.

- Levels: Typically Includes L1, L2, And Sometimes L3 Caches.

- **Impact:** Reduces Latency By Minimizing The Time Needed To Access Data From Main Memory, Thereby Improving Performance.

#### 6. Memory Hierarchy:

- **Definition:** The Organization Of Different Types Of Memory (Registers, Cache, RAM, And Secondary Storage) Based On Speed, Cost, And Size.

- **Impact:** Optimizes The Trade-Off Between Performance And Cost By Providing Faster Access To Frequently Used Data.

#### 7. Bus Speed And Bandwidth:

- **Definition:** The Speed And Capacity Of The Bus System To Transfer Data Between The CPU, Memory, And Peripherals.

- Impact: Higher Bus Speeds And Wider Buses Improve Data Transfer Rates, Enhancing Overall System Performance.

#### 8. I/O Operations:

- **Definition:** The Methods And Speed Of Data Transfer Between The Computer And External Devices.

- **Techniques:** Includes Programmed I/O, Interrupt-Driven I/O, And Direct Memory Access (DMA).

- Impact: Efficient I/O Operations Reduce Bottlenecks And Improve System Responsiveness.

#### 9. Branch Prediction:

- **Definition:** A Technique Used By Cpus To Guess The Outcome Of Conditional Operations To Improve Instruction Flow In Pipelines.

- Impact: Reduces The Number Of Stalls And Flushes In The Pipeline, Improving Execution Efficiency.

#### **10.** Power Efficiency:

- Definition: The Ratio Of Performance To Power Consumption.

- **Impact:** Critical For Battery-Operated Devices And Environmentally Friendly Computing. Balancing Performance With Power Efficiency Is Key For Sustainable Computing.

#### **Performance Metrics:**

- **Throughput:** The Number Of Tasks Or Instructions A System Can Process In A Given Amount Of Time (E.G., Instructions Per Second).

- Latency: The Time It Takes To Complete A Single Task Or Instruction From Start To Finish.

- MIPS (Million Instructions Per Second): A Measure Of The Execution Speed Of A CPU.

- FLOPS (Floating Point Operations Per Second): A Measure Of Computational Performance In Scientific Calculations.

- **Benchmarking:** Standardized Tests Used To Compare The Performance Of Different Systems (E.G., SPEC Benchmarks).

#### Performance Optimization Techniques:

- **Optimizing Algorithms:** Using More Efficient Algorithms To Reduce The Number Of Instructions And Improve Performance.

- Enhancing Compiler Techniques: Using Advanced Compiler Optimizations To Generate More Efficient Machine Code.

- Load Balancing: Distributing Workloads Evenly Across Multiple Processors Or Systems To Avoid Bottlenecks.

- Improving Memory Management: Efficient Use Of Memory And Cache To Reduce Access Times And Avoid Thrashing.

- Upgrading Hardware Components: Using Faster Cpus, More RAM, Ssds Instead Of Hdds, And Faster Network Interfaces.

Diagram Of Performance Factors In A Computer System:

| ++                                                                                           |

|----------------------------------------------------------------------------------------------|

| ++<br>  Performance  <br>++                                                                  |

| ++ ++ ++ ++ ++  <br>    Clock Speed     Pipelining     Parallelism     Cache                 |

| ++ ++ ++ ++ ++ ++  <br>  ++ ++ ++                                                            |

| <pre></pre>                                                                                  |

| ++ ++ ++ ++ ++  <br>  ++ ++ ++ ++                                                            |

| Branch     Power     Optimizing     Load    <br>    Prediction     Efficiency     Algorithms |

| ++ ++ ++ ++ ++ ++  <br>++                                                                    |

| ***                                                                                          |

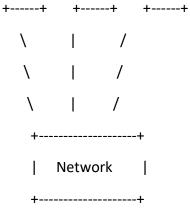

## MULTIPROCESSORS:

#### Definition:

Multiprocessors Are Systems With Multiple Cpus (Central Processing Units) That Share A Common Memory Space And Are Managed By A Single Operating System. They Are Also Known As Tightly Coupled Systems.

#### Types Of Multiprocessors:

**1. Symmetric Multiprocessing (SMP):**- All Processors Share A Single Memory And Are Equal In Their Capability To Access I/O Devices And Execute Processes.- The Operating System Manages All Processors, And Tasks Can Be Dynamically Assigned To Any Processor.

#### 2. Asymmetric Multiprocessing (AMP):

- One Processor (Master) Controls The System And All Others (Slaves) Execute Tasks Assigned By The Master.

- Common In Systems Where One Processor Handles Most Of The System's Administrative Tasks.

#### **Key Characteristics:**

- **Shared Memory:** All Processors Have Direct Access To A Common Memory Space, Allowing For Efficient Communication And Data Sharing.

- **Single Operating System:** Managed By A Single OS, Which Handles Process Scheduling And Memory Management.

- **Communication:** Via Shared Memory, Making It Easier And Faster But Also Requiring Mechanisms To Handle Memory Consistency And Synchronization.

#### Advantages:

- Easier To Program Due To The Shared Memory Model.

- Faster Communication Between Processors Compared To Multicomputers.

#### Disadvantages:

- Scalability Is Limited By Memory Bandwidth And The Complexity Of Maintaining Memory Coherence.

- Higher Risk Of Contention For Shared Resources.

#### **Applications:**

- General-Purpose Computing, Servers, Real-Time Systems, And High-Performance Computing Tasks.

Diagram Of A Multiprocessor System:

```

+-----+

| Shared Memory |

+-----+

|

+-----+

```

| | | +-----+ +-----+ |CPU1| |CPU2| |CPU3| +-----+ +-----+

#### Multicomputers

#### Definition:

Multicomputers Are Systems With Multiple Cpus, Each Having Its Own Private Memory. They Are Connected Via A Network And Do Not Share Memory. These Systems Are Also Known As Loosely Coupled Systems Or Distributed Systems.

#### **Key Characteristics:**

- **Distributed Memory:** Each Processor Has Its Own Local Memory, And Processors Communicate By Passing Messages Over A Network.

- Independent Operating Systems: Each Processor Typically Runs Its Own Operating System Instance.

- Communication: Via Message Passing, Requiring Explicit Communication Protocols.

#### **Types Of Multicomputers:**

#### **1. Cluster Computing:**

- A Group Of Linked Computers (Nodes) That Work Together As A Single System.

- Nodes Are Typically Homogeneous And Located In Close Physical Proximity.

#### 2. Grid Computing:

- A Distributed Network Of Computers, Often Geographically Dispersed, Working Together To Perform Large Tasks.

- Nodes Are Heterogeneous And Can Be Dynamically Added Or Removed.

#### 3. Massively Parallel Processors (MPP):

- Systems With A Large Number Of Processors Connected By A High-Speed Network.

- Each Processor Operates Independently But Cooperatively On A Parallel Application.

#### Advantages:

- Highly Scalable As New Processors Can Be Added Without Major Changes.

- Reduced Contention For Memory As Each Processor Has Its Own Memory.

#### **Disadvantages:**

- More Complex To Program Due To The Need For Explicit Message Passing.

- Higher Communication Overhead Compared To Shared Memory Systems.

#### **Applications:**

- Scientific Computing, Large-Scale Simulations, Distributed Databases, And Applications Requiring High Levels Of Parallelism.

Diagram Of A Multicomputer System:

•••

| CPU 1 |<---> | CPU 2 |<---> | CPU 3 |

+----+ +----+ +----+

|Memory | |Memory | Memory |

•••

Comparison Of Multiprocessors And Multicomputers:

| Feature                         | Multiprocessors             | Multicomputers                   |  |

|---------------------------------|-----------------------------|----------------------------------|--|

|                                 |                             |                                  |  |

| Memory Model                    | Shared Memory               | Distributed Memory               |  |

| Communication                   | Shared Memory               | Message Passing                  |  |

| Scalability<br>                 | Limited By Shared Memory Bo | ottlenecks   Highly Scalable     |  |

| Complexity<br>(Message Passing) | Easier To Program           | More Complex Programming         |  |

| Latency<br>                     | Lower Communication Latenc  | y   Higher Communication Latency |  |

| Operating System | Single OS Managing All Processors | Independent OS Instances Per Processor |

| Typical Use Cases | Servers, High-Performance Computing | Scientific Computing, Large-Scale Simulations, Grid Computing |

#### HISTORICAL PERSPECTIVE

The Historical Perspective In Computer Organization (CO) Highlights The Evolution Of Computer Architecture, Systems, And Technologies Over Time. This Journey Reflects The Advancements In Hardware, Software, And Overall Computational Capabilities. Below Is An Overview Of The Significant Eras And Milestones In The History Of Computer Organization:

#### 1. First Generation (1940s - 1950s): Vacuum Tubes

#### **Key Characteristics:**

- Technology: Vacuum Tubes.

- Memory: Magnetic Drums And Delay Lines.

- Input/Output: Punched Cards And Paper Tape.

- Programming Languages: Machine Language And Assembly Language.

Notable Computers:

- ENIAC (1945): The First General-Purpose Electronic Digital Computer.

- UNIVAC I (1951): The First Commercial Computer Produced In The United States.

#### Impact:

- Laid The Foundation For Digital Computing.

- Primarily Used For Scientific Calculations And Military Applications.

#### 2. Second Generation (1950s - 1960s): Transistors

#### **Key Characteristics:**

- Technology: Transistors Replaced Vacuum Tubes.

- Memory: Magnetic Core Memory.

- Input/Output: Magnetic Tape And Disk Storage.

- Programming Languages: Assembly Language, Fortran, COBOL.

#### Notable Computers:

- IBM 1401 (1959): Widely Used For Business Applications.

- CDC 1604 (1959): One Of The First Computers To Use Transistors.

#### Impact:

- Increased Reliability, Smaller Size, And Lower Heat Generation Compared To Vacuum Tubes.

- Broadened The Use Of Computers To Business Applications.

#### 3. Third Generation (1960s - 1970s): Integrated Circuits

#### Key Characteristics:

- Technology: Integrated Circuits (Ics) Combining Multiple Transistors On A Single Chip.

- Memory: Semiconductor Memory.

- Input/Output: More Sophisticated Storage Devices (Hard Drives).

- Programming Languages: Introduction Of Higher-Level Languages Like BASIC, C.

#### Notable Computers:

- IBM System/360 (1964): A Family Of Computers With A Compatible Architecture.

- DEC PDP-8 (1965): Popularized The Minicomputer.

#### Impact:

- Significant Reduction In Size And Cost.

- Introduction Of Multiprogramming And Time-Sharing Systems.

- Computers Became More Accessible To Smaller Businesses And Academic Institutions.

### 4. Fourth Generation (1970s - Present): Microprocessors

#### **Key Characteristics:**

- Technology: Microprocessors With Millions Of Transistors On A Single Chip.

- Memory: DRAM (Dynamic RAM), Ssds (Solid State Drives).

- Input/Output: GUI (Graphical User Interface), Network Interfaces.

- Programming Languages: Proliferation Of High-Level Languages (C++, Java, Python).

### Notable Computers:

- Intel 4004 (1971): The First Microprocessor.

- IBM PC (1981): Standardized The Personal Computer.

- Apple Macintosh (1984): Popularized The Graphical User Interface.

#### Impact:

- Personal Computing Revolution, Making Computers Ubiquitous In Homes And Offices.

- Development Of Networks, The Internet, And Mobile Computing.

- Ongoing Advancements In Parallel Processing, Multi-Core Processors, And Gpus.

#### 5. Fifth Generation And Beyond: Artificial Intelligence And Quantum Computing

#### **Key Characteristics:**

- Technology: AI Accelerators, Quantum Processors.

- Memory: Quantum Memory, Neuromorphic Memory.

- Input/Output: Natural Language Processing, Advanced Sensor Interfaces.

- **Programming Languages:** Languages And Frameworks For AI And Quantum Computing (E.G., Tensorflow, Qiskit).

#### Notable Developments:

- AI Systems: Specialized Hardware For Machine Learning And Neural Networks (E.G., Google's TPU, NVIDIA's Gpus).

- Quantum Computers: Experimental Quantum Processors From IBM, Google, And Other Research Institutions.

#### Impact:

- Al Is Transforming Industries Through Machine Learning, Deep Learning, And Data Analytics.

- Quantum Computing Promises To Solve Problems Intractable For Classical Computers.

#### Historical Milestones In Computer Organization:

- 1. 1940s: Development Of The First Electronic Digital Computers (ENIAC).

- 2. 1950s: Transition From Vacuum Tubes To Transistors (IBM 1401).

- 3. 1960s: Introduction Of Integrated Circuits And The Rise Of Mainframes (IBM System/360).

- 4. 1970s: Emergence Of Microprocessors And Personal Computing (Intel 4004).

- 5. **1980s:** Proliferation Of Personal Computers (IBM PC, Apple Macintosh).

- 6. 1990s: Growth Of The Internet And Networking.

- 7. 2000s: Advances In Multi-Core Processors And Mobile Computing.

- 8. 2010s: Rise Of Cloud Computing, Big Data, And AI.

- 9. 2020s: Ongoing Research And Development In Quantum Computing And AI Accelerators.

#### MACHINE INSTRUCTIONS AND PROGRAMS:

Machine Instructions Are The Fundamental Units Of Execution In A Computer's CPU, While Programs Are Collections Of These Instructions That Perform Specific Tasks. Let's Delve Deeper Into The Relationship Between Machine Instructions And Programs, How Machine Instructions Work, How Programs Are Structured, And How They Are Executed By The CPU.

## **Machine Instructions:**

Machine Instructions Are Binary Codes That The CPU Can Execute Directly. Each Instruction Tells The CPU To Perform A Specific Operation, Such As Arithmetic, Data Movement, Or Control Operations. These Instructions Are Specific To The CPU's Architecture, Meaning Different CPU Architectures (E.G., X86, ARM) Have Different Sets Of Machine Instructions.

## COMPONENTS OF MACHINE INSTRUCTIONS

**1. Opcode (Operation Code):** Specifies The Operation To Be Performed (E.G., ADD, SUB, LOAD).

**2. Operands:** Specifies The Data To Be Operated On. Operands Can Be Immediate Values, Registers, Or Memory Addresses.

**3. Addressing Mode:** Defines How The Operands Are Accessed (E.G., Direct, Indirect, Immediate).

## **Example Of Machine Instructions**

## Here's A Simple Example Of Machine Instructions For An Imaginary CPU:

- ADD R1, R2, R3: Adds The Contents Of Register R2 And R3, And Stores The Result In R1.

- LOAD R1, 1000: Loads The Contents Of Memory Address 1000 Into Register R1.

- STORE R1, 1000: Stores The Contents Of Register R1 Into Memory Address 1000.

- JMP 200: Jumps To The Instruction Located At Memory Address 200.

## Programs

A Program Is A Sequence Of Machine Instructions That Accomplishes A Specific Task. Programs Can Be Written In High-Level Programming Languages (E.G., C, Python), Which Are Then Compiled Or Interpreted Into Machine Instructions That The CPU Can Execute.

## **Example Program**

Consider A Simple Program Written In Assembly Language (A Human-Readable Representation Of Machine Instructions) For An Imaginary CPU. This Program Adds Two Numbers And Stores The Result In Memory.

```Assembly

LOAD R1, 1000 ; Load The First Number From Memory Address 1000 Into R1

LOAD R2, 1001 ; Load The Second Number From Memory Address 1001 Into R2

ADD R3, R1, R2 ; Add The Contents Of R1 And R2, Store The Result In R3

STORE R3, 1002 ; Store The Result From R3 Into Memory Address 1002

## **Execution Of Programs**

## The CPU Executes Programs Through A Cycle Known As The Fetch-Decode-Execute Cycle:

1. Fetch: The CPU Fetches The Next Instruction From Memory.

2. **Decode:** The CPU Decodes The Fetched Instruction To Determine What Operation To Perform And What Operands To Use.

3. **Execute:** The CPU Executes The Decoded Instruction, Performing The Specified Operation.

## **Detailed Execution Process**

## 1. Fetch:

- The Program Counter (PC) Holds The Address Of The Next Instruction.

- The CPU Fetches The Instruction From This Address.

2. **Decode:-** The CPU Decodes The Instruction To Understand The Opcode And The Operands.

- This Involves Breaking Down The Binary Instruction Into Its Components.

## 3. Execute:

- The CPU Performs The Operation Specified By The Opcode Using The Specified Operands.

- This Could Involve Arithmetic Operations, Data Movement, Or Control Flow Changes (Like Jumps).

Example: Adding Two Numbers

## Let's Break Down The Execution Of The Example Program That Adds Two Numbers:

## 1. Fetch LOAD R1, 1000:

- The PC Points To The Address Of The First Instruction.

- The CPU Fetches The Instruction `LOAD R1, 1000`.

## 2. Decode LOAD R1, 1000:

- The CPU Decodes The Instruction: `LOAD` Means Load A Value From Memory.

- Operand R1 Is The Destination Register, And 1000 Is The Memory Address.

## 3. Execute LOAD R1, 1000:

- The CPU Loads The Value From Memory Address 1000 Into Register R1.

## 4. Fetch LOAD R2, 1001:

- The PC Is Incremented To Point To The Next Instruction.

- The CPU Fetches The Instruction `LOAD R2, 1001`.

## 5. Decode And Execute LOAD R2, 1001:

- Similar To The First Load Instruction, The CPU Loads The Value From Memory Address 1001 Into Register R2.

## 6. Fetch ADD R3, R1, R2:

- The PC Is Incremented To Point To The Next Instruction.

- The CPU Fetches The Instruction `ADD R3, R1, R2`.

## 7. Decode ADD R3, R1, R2:

- The CPU Decodes The Instruction: `ADD` Means Add The Values In Two Registers.

- Operands Are R1 And R2, And The Result Is To Be Stored In R3.

## 8. Execute ADD R3, R1, R2:

- The CPU Adds The Values In R1 And R2 And Stores The Result In R3.

## 9. Fetch STORE R3, 1002:

- The PC Is Incremented To Point To The Next Instruction.

- The CPU Fetches The Instruction `STORE R3, 1002`.

## 10. Decode And Execute STORE R3, 1002:

- The CPU Decodes The Instruction: `STORE` Means Store A Value Into Memory.

- Operand R3 Is The Source Register, And 1002 Is The Memory Address.

- The CPU Stores The Value In R3 Into Memory Address 1002.

## **MEMORY LOCATION AND ADDRESSES:**

Memory Locations And Addresses Are Fundamental Concepts In Computer Architecture And Organization, Defining How Data Is Stored And Accessed In A Computer's Memory Hierarchy. Let's Explore These Concepts In Detail:

## **Memory Locations**

A Memory Location Refers To A Specific Location In The Computer's Memory Where Data Can Be Stored Or Retrieved. It Is Identified By A Unique Numeric Address, Which Allows The CPU To Access And Manipulate Data Stored At That Location.

## **Characteristics:**

1. **Size:** Each Memory Location Typically Holds A Fixed Amount Of Data, Often Measured In Bytes (E.G., 1 Byte, 4 Bytes).

2. **Addressability:** Memory Locations Are Individually Accessible By Their Addresses, Allowing The CPU To Read Or Write Data Directly.

3. **Numbering:** Memory Locations Are Sequentially Numbered, Starting From Zero Up To The Maximum Addressable Range Supported By The System's Memory Architecture.

## Memory Addresses

A Memory Address Is A Numeric Value Used To Uniquely Identify A Memory Location In A Computer's Memory System. It Serves As A Reference Point For The CPU To Locate Specific Data In Memory For Processing.

## **Characteristics:**

1. **Representation:** Memory Addresses Are Typically Represented In Binary Form, Corresponding To The Physical Or Virtual Memory Space Of The System.

2. Size: The Size Of A Memory Address (Address Bus Width) Determines The Maximum Amount Of Memory That Can Be Addressed By The CPU. For Example, A 32-Bit Address Bus Can Address Up To \(2^{32}\) Memory Locations (4 GB), And A 64-Bit Address Bus Can Address Up To \(2^{64}\) Memory Locations (Over 16 Exabytes).

3. Address Space: Refers To The Total Range Of Memory Addresses That A CPU Or A Program Can Access. It Is Constrained By The Width Of The Address Bus And The Memory Management Capabilities Of The System.

## Types Of Memory Addresses:

## 1. Physical Address:

- A Physical Address Directly Corresponds To A Specific Location In The Physical Memory (RAM) Of The Computer.

- Used By The CPU To Access Data And Instructions During Normal Operation.

2. Virtual Address: - A Virtual Address Is Used In Systems With Virtual Memory Management, Where Physical Memory Addresses Are Abstracted And Managed By The Operating System.

- Translated Into Physical Addresses By The Memory Management Unit (MMU) Of The CPU.

## **ADDRESSING MODES:**

Computers Use Different Addressing Modes To Specify How Memory Addresses Are Calculated Or Interpreted When Accessing Data. Common Addressing Modes Include:

1. Direct Addressing: The Operand Specifies A Memory Address Directly.

- Example: `LOAD R1, 1000` (Load The Contents Of Memory Address 1000 Into Register R1).

2. Indirect Addressing: The Operand Specifies A Memory Address That Contains The Actual Memory Address Of The Data.

- Example: `LOAD R1, (R2)` (Load The Contents Of The Memory Address Stored In R2 Into R1).

3. **Indexed Addressing:** The Operand's Effective Address Is Generated By Adding A Constant Value Or The Contents Of A Register To A Base Address.

- Example: `LOAD R1, 1000(R2)` (Load The Contents Of Memory Address 1000 Plus The Value In R2 Into R1).

### **MEMORY ORGANIZATION:**

Memory In A Computer System Is Organized Hierarchically Into Different Levels:

1. **Registers:** Fastest And Smallest Storage Directly Accessible By The CPU.

2. **Cache Memory:** Small But Faster Than Main Memory, Used To Temporarily Store Frequently Accessed Data.

3. **Main Memory (RAM):** Larger Storage For Programs And Data During Execution, Accessed Directly By The CPU.

4. **Secondary Storage:** Non-Volatile Storage Devices Like Hard Drives And Ssds, Used For Long-Term Data Storage.

### ASSEMBLE LANGUAGE:

In The Context Of Computer Organization (CO), Assembly Language Plays A Crucial Role As It Directly Interfaces With The Hardware Components Of A Computer System. Let's Explore How Assembly Language Fits Into Computer Organization And Its Significance:

Role Of Assembly Language In Computer Organization

### 1. Direct Hardware Interaction:

- Assembly Language Allows Programmers To Interact Directly With The Hardware Components Of A Computer, Such As Registers, Memory, And I/O Devices.

- This Direct Interaction Is Essential For Tasks Like Device Driver Development, Low-Level System Programming, And Real-Time Embedded Systems Where Precise Control Over Hardware Is Necessary.

### 2. Representation Of Machine Instructions:

- Assembly Language Provides A Human-Readable Representation Of Machine Instructions Specific To A Particular CPU Architecture.

- Each Assembly Instruction Corresponds Directly To A Machine Instruction That The CPU Can Execute, Facilitating Low-Level Programming.

#### 3. Efficiency And Optimization:

- Programs Written In Assembly Language Can Be Highly Optimized For Performance And Memory Usage.

- Assembly Programmers Have Fine-Grained Control Over The Use Of CPU Registers, Memory Access Patterns, And Instruction Sequences, Leading To Faster Execution Of Critical Code Sections.

#### 4. Understanding Computer Architecture:

- Learning Assembly Language Enhances Understanding Of Computer Architecture Principles, Including CPU Operation, Memory Hierarchy, Instruction Pipelining, And Cache Behavior.

- It Bridges The Gap Between High-Level Programming Languages And The Underlying Hardware Architecture, Providing Insights Into How Software Instructions Are Executed At The Machine Level.

#### **Components And Features Of Assembly Language In CO**

#### 1. Instruction Set Architecture (ISA):

- Assembly Language Instructions Directly Reflect The Instruction Set Architecture (ISA) Of A CPU.

- ISA Defines The Set Of Instructions That The CPU Can Execute And How They Are Encoded And Interpreted.

### 2. Registers And Memory Access:

- Assembly Language Instructions Manipulate CPU Registers And Directly Access Memory Locations Using Specific Addressing Modes (E.G., Direct, Indirect, Indexed).

- This Level Of Control Is Crucial For Managing Data And Program Flow Efficiently.

### 3. Assembler And Linker:

- An Assembler Is A Program That Translates Assembly Language Code Into Machine Code (Binary Instructions) That The CPU Can Execute.

- A Linker Combines Object Files (Resulting From Assembling Source Code) With Libraries And Resolves External References To Generate Executable Programs.

### 4. Development And Debugging Tools:

- Assembly Language Programming Typically Involves The Use Of Specialized Tools For Development, Debugging, And Performance Profiling.

- Debugging Tools Help Programmers Trace Code Execution, Inspect Register Contents, And Analyze Memory Access Patterns.

### Example Of Assembly Language Use In CO

Consider A Simple Assembly Language Program That Calculates The Factorial Of A Number:

```Assembly

Section .Data

N Db 5 ; Define Variable N With Initial Value 5

Section .Text

**Global**\_Start

\_Start:

; Initialize Registers

Mov Ecx, 1 ; Initialize Counter (Ecx) To 1

Mov Eax, 1 ; Initialize Result (Eax) To 1

Calculate\_Factorial:

Cmp Ecx, [N] ; Compare Ecx (Counter) With N

Jg End\_Calc ; Jump To End\_Calc If Counter > N

Imul Eax, Ecx ; Multiply Result (Eax) By Counter (Ecx)

Inc Ecx ; Increment Counter (Ecx) Jmp Calculate\_Factorial ; Jump To Calculate\_Factorial

End\_Calc:

; Store Result In Memory Or Print It

; Example: Store Result In A Specific Memory Location

Mov [Factorial\_Result], Eax ; Store Result In Memory Location Factorial\_Result

; Exit The Program

Mov Eax, 1 ; System Call Number For Exit

Xor Ebx, Ebx ; Status Code 0

Int 0x80 ; Invoke Operating System To Exit

•••

# **Benefits And Challenges**

- Benefits:

- Provides Direct Control Over Hardware.

- Enables Optimization For Performance-Critical Applications.

- Enhances Understanding Of Computer Architecture.

- Challenges:

- More Complex And Error-Prone Than High-Level Languages.

- Not Easily Portable Across Different CPU Architectures.

- Requires Deep Knowledge Of CPU Architecture And Instruction Set.

#### **BASIC INPUT AND OUTPUT OPERATIONS:**

In The Context Of Computer Organization (CO), Basic Input And Output (I/O) Operations Are Fundamental For Interacting With Users And External Devices. These Operations Typically Involve Reading Data From Input Sources And Writing Data To Output Destinations. Here's How Input And Output Operations Are Handled At A Fundamental Level In CO:

### **Basic Input Operations:**

### 1. Keyboard Input:

- In CO, Keyboard Input Is Often Handled Through Low-Level Routines Or System Calls That Interact With The Operating System's Input Handling Mechanisms.

- Programs Typically Request User Input, Which Is Then Processed By The Operating System And Delivered To The Program.

### 2. File Input:

- Input From Files Is Crucial In CO For Processing Data Stored On Disk Or In Secondary Storage Devices.

- Programs Utilize File I/O Operations To Read Data From Files, Which Involves Accessing Specific Addresses Or Memory-Mapped Locations Corresponding To File Contents.

### **Basic Output Operations**

### 1. Console Output:

- Displaying Output On The Console (Screen) Is A Primary Form Of Communication From Programs To Users In CO.

- Programs Use System Calls Or Direct Memory Access To Write Characters Or Data To Specific Locations That Correspond To The Display Output.

### 2. File Output:

- Writing Data To Files Is Essential For Saving Program Results, Logging Information, Or Storing Configurations In CO.

- Programs Interact With The Operating System's File Management Services To Create, Write To, And Close Files, Ensuring Data Integrity And Accessibility. System Calls And Hardware Interaction

- **System Calls:** In CO, Input And Output Operations Often Involve System Calls (Apis) Provided By The Operating System. These Calls Abstract Low-Level Hardware Interactions, Providing A Standardized Interface For Programs To Perform I/O Operations.

- **Device Interaction:** Input And Output Operations May Involve Direct Interaction With Peripheral Devices Such As Keyboards, Monitors, Disk Drives, And Network Interfaces. These Interactions Are Managed By The Operating System To Ensure Proper Coordination And Data Integrity.

Example In Assembly Language (X86 Architecture)

Here's A Simple Example In Assembly Language (NASM Syntax For X86 Architecture) Demonstrating Basic Console Input And Output Operations:

```Assembly

Section .Data

Message Db 'Enter A Number: ', 0 ; Define A Null-Terminated String Message

Section .Bss

Num Resb 10 ; Reserve 10 Bytes For Storing User Input (Assuming A Number Input)

Section .Text

Global \_Start

\_Start:

; Print Message To Console

Mov Eax, 4 ; System Call For Write (Stdout)

Mov Ebx, 1 ; File Descriptor 1 (Stdout)

Mov Ecx, Message ; Address Of Message To Print

- Mov Edx, 15 ; Message Length

- Int 0x80 ; Invoke Syscall

- ; Read Input From Keyboard

- Mov Eax, 3 ; System Call For Read (Stdin)

- Mov Ebx, 0 ; File Descriptor 0 (Stdin)

- Mov Ecx, Num ; Buffer To Store Input

- Mov Edx, 10 ; Maximum Bytes To Read

- Int 0x80 ; Invoke Syscall

- ; Print Newline Character

- Mov Eax, 4 ; System Call For Write (Stdout)

- Mov Ebx, 1 ; File Descriptor 1 (Stdout)

- Mov Ecx, Newline ; Address Of Newline Character

- Mov Edx, 1 ; Length Of Newline Character

- Int 0x80 ; Invoke Syscall

#### ; Exit The Program

- Mov Eax, 1 ; System Call Number For Exit

- Xor Ebx, Ebx ; Exit Status Code 0

- Int 0x80 ; Invoke Syscall

Section .Data

Newline Db 10 ; Define Newline Character (ASCII 10)

•••

### Stacks:

### **1. Definition And Characteristics:**

- LIFO (Last-In-First-Out) Structure: Stacks Follow The Principle Where The Last Element Added Is The First One To Be Removed.

- **Operations:** Stacks Typically Support Two Main Operations:

- Push: Adds An Element To The Top Of The Stack.

- **Pop:** Removes And Returns The Top Element From The Stack.

- Implementation: Stacks Can Be Implemented Using Arrays Or Linked Lists.

# 2. Usage In CO:

- Function Call Stack: Every Time A Function Is Called, Its Local Variables And Execution Context Are Pushed Onto The Stack. When The Function Completes, It Is Popped Off The Stack, Allowing The Program To Return To The Previous Function.

- **Memory Management:** Stacks Are Used By Compilers And Operating Systems To Manage Memory Allocation For Local Variables And Function Calls.

- Interrupt Handling: Stacks Are Crucial In Storing The State Of Interrupted Processes Or Threads, Allowing For Seamless Context Switching.

# 3. Example Scenario:

- Function Call: When A CO Program Calls A Function, Its Arguments, Return Address, And Local Variables Are Pushed Onto The Stack. As The Function Completes Execution, It Pops These Elements Off The Stack To Resume The Caller's Execution.

# **QUEUES:**

# **1. Definition And Characteristics:**

- **FIFO (First-In-First-Out) Structure:** Queues Follow The Principle Where The First Element Added Is The First One To Be Removed.

- **Operations:** Queues Typically Support Two Primary Operations:

- Enqueue: Adds An Element To The Back Of The Queue.

- Dequeue: Removes And Returns The Front Element Of The Queue.

- Implementation: Queues Can Be Implemented Using Arrays Or Linked Lists.

- 2. Usage In CO:

- Job Scheduling: Queues Are Used In Operating Systems To Schedule Tasks Or Processes For Execution Based On Priority Or Arrival Time.

- **Buffering:** Queues Are Used In Communication Systems (Like Networking) For Managing Data Packets Awaiting Transmission.

- **Print Spooling:** Queues Are Used In Printing Systems To Manage Multiple Print Jobs In A Sequence.

## 3. Example Scenario:

- **Operating System Scheduler:** In A CO Environment, The Operating System Uses A Queue-Based Scheduler To Manage Multiple Processes, Ensuring Fairness And Efficient Resource Allocation.

### **SUB ROUTINES**

Subroutines, Also Known As Subprograms Or Procedures, Are Essential Components Of Programming In Computer Organization (CO). They Allow Programmers To Modularize Their Code, Promote Reusability, And Facilitate Structured Program Design. Let's Explore Subroutines In CO In Detail:

**Definition And Characteristics**

# 1. Definition:

- **Subroutine:** A Subroutine Is A Named Block Of Code Within A Program That Performs A Specific Task. It Can Be Called (Invoked) Multiple Times From Different Parts Of The Program.

### 2. Characteristics:

- **Modularity:** Subroutines Promote Modular Programming By Encapsulating Specific Functionality, Making Code More Organized And Easier To Manage.

- **Reusability:** Once Defined, Subroutines Can Be Called From Different Parts Of The Program, Avoiding Code Duplication And Promoting Efficient Use Of Resources.

- **Parameter Passing:** Subroutines Can Accept Parameters (Inputs) And Return Values (Outputs) To And From The Calling Code, Facilitating Flexible Data Handling.

# **Types Of Subroutines**

# 1. Procedures:

- Procedures Are Subroutines That Perform A Task Without Returning A Value. They Are Typically Used For Actions Or Operations That Modify Data Or Perform Computations.

# 2. Functions:

- Functions Are Subroutines That Return A Value Upon Completion. They Are Used For Computations That Produce A Result, Which Is Then Used By The Calling Code.

# Implementation And Usage In CO

# 1. Calling Convention:

- **Stack-Based Parameters:** In CO, Parameters Are Often Passed To Subroutines Using The Stack. This Involves Pushing Parameters Onto The Stack Before Calling The Subroutine And Popping Them Off Within The Subroutine.

# 2. Memory Management:

- **Stack Frame:** Each Subroutine Invocation Typically Creates A Stack Frame, Which Includes Parameters, Local Variables, And Return Addresses. The Stack Frame Is Managed By The Compiler Or Runtime Environment.

# 3. Instruction Set Architecture (ISA):

- CO Systems Provide Specific Instructions And Addressing Modes For Subroutine Calls And Returns. These Instructions Ensure Proper Execution Flow And Manage Program State.

# Example Scenario

Consider A Simple CO Program With A Subroutine To Calculate The Factorial Of A Number:

```Assembly Section .Data N Db 5 ; Define Variable N With Initial Value 5 Section .Text Global Start Start: ; Call Subroutine To Calculate Factoria Mov Eax, N ; Move N Into Register Eax Call Factorial ; Call Subroutine Factorial ; Result Is Now In Eax ; Print The Result ; (Assuming A Function To Print Integer Is Available) Mov Ebx, Eax ; Move Result (Eax) To Ebx (For Print) Call Print\_Integer ; Call Subroutine To Print Integer ; Ebx May Hold The Return Value From Print Integer If Applicable ; Exit The Program Mov Eax, 1 ; System Call Number For Exit Xor Ebx, Ebx ; Status Code 0 ; Invoke Operating System To Exit Int 0x80 Factorial: Push Ebp ; Save Current Base Pointer Mov Ebp, Esp ; Set New Base Pointer Mov Ecx, [Ebp+8] ; Load Parameter N From Stack Mov Eax, 1 ; Initialize Result To 1 Calculate Factorial: Cmp Ecx, 1 ; Compare Ecx (Counter) With 1

```

Jle End_Factorial ; Jump To End_Factorial If Counter <= 1

Imul Eax, Ecx ; Multiply Result (Eax) By Counter (Ecx)

Dec Ecx ; Decrement Counter (Ecx)

Jmp Calculate_Factorial ; Jump To Calculate_Factorial

End_Factorial:

Mov Esp, Ebp ; Restore Stack Pointer

Pop Ebp ; Restore Base Pointer

Ret ; Return To Caller

```

### **Benefits Of Subroutines In CO**

- **Code Reusability:** Subroutines Allow For The Reuse Of Code Blocks Across Different Parts Of The Program, Reducing Redundancy And Improving Maintainability.

- **Modular Design:** By Breaking Down Tasks Into Smaller, Manageable Units (Subroutines), Programmers Can Focus On Specific Functionalities, Promoting Clear And Structured Program Design.

- Efficient Resource Utilization: Subroutines Optimize Program Execution By Reducing Memory Usage And Enhancing Code Organization, Leading To Improved Performance And Scalability.

#### **ADDITIONAL INSTRUCTIONS:**

#### **1. Additional Machine Instructions**

In CO, The Term "Additional Instructions" Often Refers To New Instructions Added To The Instruction Set Architecture (ISA) Of A Processor. These Instructions Expand The Capabilities Of The CPU, Providing More Efficient Ways To Perform Specific Operations Or Improving Overall Performance. Examples Include:

- Vector Instructions: Instructions That Operate On Multiple Data Elements Simultaneously, Often Used In Multimedia And Scientific Applications To Accelerate Processing. - **SIMD (Single Instruction, Multiple Data) Instructions:** Instructions That Perform The Same Operation On Multiple Data Elements In Parallel, Optimizing Tasks Like Graphics Processing And Signal Processing.

- Floating-Point Instructions: Instructions That Handle Floating-Point Arithmetic Operations More Efficiently Than Traditional Integer Operations.

# 2. Additional System-Level Instructions

At A Higher Level, "Additional Instructions" May Refer To System-Level Instructions Or Apis Provided By The Operating System Or Hardware Platform. These Instructions Facilitate Interactions With Peripherals, Manage Memory, Or Control Hardware Devices. Examples Include:

- **System Calls:** Instructions Used To Request Services From The Operating System, Such As File Operations, Process Management, And Network Communications.

- **Direct Memory Access (DMA) Instructions:** Instructions That Allow Devices To Transfer Data Directly To And From Memory Without CPU Intervention, Enhancing Performance In Data-Intensive Operations.

- I/O Instructions: Instructions That Facilitate Input And Output Operations, Managing Communication Between The CPU And External Devices Like Disks, Keyboards, And Displays.

# 3. Additional Assembly Language Instructions

In Assembly Language Programming, "Additional Instructions" Could Refer To Custom Or Specialized Instructions Beyond The Standard Set Provided By The CPU's ISA. These Instructions May Be Implemented For Specific Tasks Or Optimizations Unique To A Particular Application Or Hardware Configuration.

# Example Scenario:

Consider An Example Where Additional SIMD Instructions Are Introduced To Accelerate Image Processing Tasks On A CO System:

```Assembly

Section .Data

Src\_Data Db 0x1, 0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8 ; Sample Source Data Dest Data Times 8 Db 0 ; Destination Data Section .Text Global Start Start: ; Load Source Data Into XMM Register Using SIMD Instructions Movdqu Xmm0, [Src\_Data] ; Load 128-Bit Data From Src\_Data Into Xmm0 ; Perform SIMD Operation (E.G., Add) On Xmm0 Paddb Xmm0, Xmm0 ; Add Xmm0 With Itself (Byte-Wise) ; Store The Result Back Into Memory Using SIMD Instructions Movdgu [Dest Data], Xmm0 ; Store Xmm0 Into Dest Data ; Exit The Program Mov Eax, 1 ; System Call Number For Exit Xor Ebx, Ebx ; Status Code 0 Int 0x80 ; Invoke Operating System To Exit

•••

### **Benefits And Considerations**

- **Performance:** Additional Instructions Often Improve Performance By Leveraging Hardware-Specific Optimizations Or Handling Complex Tasks More Efficiently.

- **Specialized Tasks:** They Enable The Implementation Of Specialized Algorithms And Operations That Are Not Efficiently Supported By Standard Instructions.

- **Compatibility:** Care Must Be Taken With Additional Instructions To Ensure Compatibility Across Different Hardware Platforms And Versions Of The Instruction Set Architecture. Encoding Of Machine Instructions Refers To The Representation Of Instructions In Binary Form That Processors Can Execute. This Encoding Is Fundamental To Computer Organization (CO), As It Dictates How Instructions Are Decoded And Executed By The CPU. Here's An Overview Of How Machine Instructions Are Encoded:

# 1. Instruction Set Architecture (ISA)

- **Definition:** ISA Defines The Set Of Instructions That A Processor Can Execute And How These Instructions Are Encoded In Binary Format.

- **Types Of Instructions:** Isas Typically Include Instructions For Arithmetic Operations (Add, Subtract), Logic Operations (AND, OR), Data Movement (Load, Store), Control Flow (Branch, Jump), And More Specialized Operations.

# 2. Instruction Format

- Fixed-Length Vs. Variable-Length: Instructions Can Be Of Fixed Or Variable Length Depending On The ISA Design.

- **Components:** Instructions Are Composed Of Fields That Specify The Operation Code (Opcode), Operands (Registers Or Memory Addresses), And Other Control Information.

# 3. Encoding Principles:

- Opcode: Specifies The Operation To Be Performed (E.G., Add, Subtract).

- Operands: Addresses Or Data On Which The Operation Is Performed.

- Addressing Modes: Define How Operands Are Specified (Register, Immediate Value, Indirect Addressing).

- **Control Information:** Flags Or Control Bits That Affect Instruction Execution (E.G., Condition Codes For Conditional Branches).

# 4. Example Of Instruction Encoding

Consider A Simplified Example Of Encoding An ADD Instruction In A Hypothetical 8-Bit ISA: - **Opcode For ADD:** Let's Assume ADD Has Opcode `0001`.

- Register Operand: Suppose We Have Registers Labeled `R0` To `R7`.

- Encoding Example: Adding The Contents Of `R1` To `R2` And Storing The Result In `R3`.

•••

ADD R3, R1, R2<sup>``</sup> - Binary Representation:

- Opcode `0001` (ADD Operation)

- Register `R3` Encoded As `011` (Assuming 3-Bit Register Encoding)

- Register `R1` Encoded As `001`

- Register `R2` Encoded As `010`

- Combined Binary Encoding: If We Assume A Fixed Format Of 8 Bits:

•••

0001 011 001 010

- **Decoding:** The Processor Reads This Binary Instruction, Extracts The Opcode (`0001`), And Interprets The Subsequent Fields (`011`, `001`, `010`) As Registers For The ADD Operation.

# 5. Machine Instruction Execution

- **Fetch-Decode-Execute Cycle**: During Execution, The CPU Fetches Instructions From Memory, Decodes Them Based On Their Binary Encoding, And Executes Them Using Its Internal Logic Units.

- **Pipeline Processing:** Modern Cpus Use Instruction Pipelines To Overlap Fetch, Decode, And Execute Stages For Improved Performance.

# **Benefits Of Efficient Encoding:**

- **Compactness:** Efficient Encoding Allows For Compact Representation Of Instructions, Optimizing Memory Usage And Instruction Cache Performance.

- **Speed:** Simplified Decoding And Execution Processes Contribute To Faster Program Execution.

#### ENCODING OF MACHINE INSTRUCTIONS:

Encoding Of Machine Instructions Refers To The Representation Of Instructions In Binary Form That Processors Can Execute. This Encoding Is Fundamental To Computer Organization (CO), As It Dictates How Instructions Are Decoded And Executed By The CPU. Here's An Overview Of How Machine Instructions Are Encoded:

## 1. Instruction Set Architecture (ISA)

- **Definition:** ISA Defines The Set Of Instructions That A Processor Can Execute And How These Instructions Are Encoded In Binary Format.

- **Types Of Instructions:** Isas Typically Include Instructions For Arithmetic Operations (Add, Subtract), Logic Operations (AND, OR), Data Movement (Load, Store), Control Flow (Branch, Jump), And More Specialized Operations.

## 2. Instruction Format

- Fixed-Length Vs. Variable-Length: Instructions Can Be Of Fixed Or Variable Length Depending On The ISA Design.

- **Components:** Instructions Are Composed Of Fields That Specify The Operation Code (Opcode), Operands (Registers Or Memory Addresses), And Other Control Information.

# **3. Encoding Principles**

- Opcode: Specifies The Operation To Be Performed (E.G., Add, Subtract).

- **Operands:** Addresses Or Data On Which The Operation Is Performed.

- Addressing Modes: Define How Operands Are Specified (Register, Immediate Value, Indirect Addressing).

- **Control Information:** Flags Or Control Bits That Affect Instruction Execution (E.G., Condition Codes For Conditional Branches).

# 4. Example Of Instruction Encoding

Consider A Simplified Example Of Encoding An ADD Instruction In A Hypothetical 8-Bit ISA: - Opcode For ADD: Let's Assume ADD Has Opcode `0001`.

- Register Operand: Suppose We Have Registers Labeled `R0` To `R7`.

- **Encoding Example:** Adding The Contents Of `R1` To `R2` And Storing The Result In `R3`.

• • •

ADD R3, R1, R2

•••

- Binary Representation:

- Opcode `0001` (ADD Operation)

- Register `R3` Encoded As `011` (Assuming 3-Bit Register Encoding)

- Register `R1` Encoded As `001`

- Register `R2` Encoded As `010`

- Combined Binary Encoding: If We Assume A Fixed Format Of 8 Bits:

• • • •

0001 011 001 010

- **Decoding:** The Processor Reads This Binary Instruction, Extracts The Opcode (`0001`), And Interprets The Subsequent Fields (`011`, `001`, `010`) As Registers For The ADD Operation.

# 5. MACHINE INSTRUCTION EXECUTION:

- **Fetch-Decode-Execute Cycle:** During Execution, The CPU Fetches Instructions From Memory, Decodes Them Based On Their Binary Encoding, And Executes Them Using Its Internal Logic Units.

- **Pipeline Processing:** Modern Cpus Use Instruction Pipelines To Overlap Fetch, Decode, And Execute Stages For Improved Performance.

# <u>UNIT-2</u>

## INPUT/OUTPUT/ORGANIZATION

# ACESSING I/O DEVICES:

Accessing I/O (Input/Output) Devices Is A Crucial Aspect Of Computer Architecture And Operating Systems. It Involves Communication Between The CPU And Peripheral Devices Like Keyboards, Monitors, Printers, Disk Drives, Etc. Here's An Overview Of The Key Concepts:

# 1. I/O Device Types:

- Input Devices: Devices That Send Data To The Computer (E.G., Keyboard, Mouse, Scanner).

- **Output Devices:** Devices That Receive Data From The Computer (E.G., Monitor, Printer).

- Storage Devices: Devices That Store Data (E.G., Hard Drives, Ssds).

# 2. I/O Methods:

- **Programmed I/O:** The CPU Is Responsible For Executing I/O Instructions And Actively Waits For The I/O Operation To Complete.

- Interrupt-Driven I/O: The CPU Initiates An I/O Operation And Continues With Other Tasks. When The I/O Operation Is Complete, The Device Generates An Interrupt To Signal The CPU.

- **Direct Memory Access (DMA):** A Special Control Unit Directly Transfers Data Between I/O Devices And Memory, Reducing The CPU's Involvement.

# 3. I/O Ports And Memory-Mapped I/O

- I/O Ports: Special Address Space Distinct From Memory Used To Communicate With I/O Devices.

- Memory-Mapped I/O: I/O Devices Are Treated As If They Are Part Of The Memory Address Space. This Allows Standard Instructions To Be Used For I/O Operations.

# 4. I/O Controllers:

- Hardware Components That Manage The Data Exchange Between The CPU And I/O Devices. They Often Include Buffers To Store Data Temporarily.

# 5. Device Drivers:

- Software That Provides An Interface Between The Operating System And I/O Devices, Abstracting The Hardware Details And Providing Standardized Methods For Communication.

# 6. I/O Scheduling:

- The Operating System's Method For Managing Multiple I/O Requests To Ensure Efficient And Fair Use Of I/O Resources. Common Algorithms Include First-Come-First-Served (FCFS), Shortest Seek Time First (SSTF), And Elevator (SCAN).

Detailed Steps For Accessing I/O Devices:

# Step 1: Device Initialization:

- The Operating System Initializes The Device, Setting It Up For Communication And Data Transfer.

# Step 2: Issuing Commands:

- The CPU Sends Commands To The I/O Device Via I/O Ports Or Memory-Mapped I/O Addresses.

# Step 3: Data Transfer:

- Depending On The Method Used (Programmed I/O, Interrupt-Driven I/O, Or DMA), Data Is Transferred Between The CPU/Memory And The I/O Device.

# Step 4: Handling Interrupts

- If Using Interrupt-Driven I/O, The Device Sends An Interrupt To The CPU Upon Completing The Operation. The CPU Then Executes An Interrupt Service Routine (ISR) To Handle The Event.

# Step 5: Completing The Operation:

- The Operating System Or Device Driver Performs Any Necessary Cleanup And Makes The Data Available To The Application.

## Example:

## Programmed I/O:

```Assembly

MOV DX, DATA\_PORT ; Move The Address Of The Data Port To DX

MOV AL, [DATA] ; Move Data To AL Register